## **3789**

# A frequency adaptive multiple complex coefficient filter for grid connected applications

Bachir Boumediene<sup>1</sup>, Rabah Araria<sup>1</sup>, Zakaria Chedjara<sup>1</sup>, Belkacem Mekhloufi<sup>1</sup>, Mohamed Bey<sup>1</sup>, Patrice Wira<sup>2</sup>

<sup>1</sup>L2GEGI Laboratory, Department of Electrical Engineering, Faculty of Applied Sciences, University of Tiaret, Algeria <sup>2</sup>IUT of Mulhouse, IRIMAS Laboratory, University of Haute Alsace, 61 Rue Albert Camus, Mulhouse, France

#### **Article Info**

## Article history:

Received Jul 23, 2023 Revised Apr 8, 2024 Accepted May 16, 2024

#### Keywords:

Closed loop systems

Frequency estimation

techniques

Frequency locked loop

Open-loop systems

Phase detection methods

Phase locked loop

Synchronization algorithms

#### **ABSTRACT**

In the realm of synchronization techniques, the dichotomy between open loops (OLSs) and closed loops (CLSs) presents a perennial challenge: how to enhance dynamic performance without sacrificing stability and disturbance rejection. While OLS techniques offer rapid dynamic response and unwavering stability, they often falter in non-nominal frequency scenarios. Conversely, CLS techniques grapple with the delicate balance of bolstering dynamic performance while maintaining robust stability. To surmount these obstacles, this study proposes an innovative approach: the integration of a frequency locked loop (FLL) as a secondary frequency within synchronization structures, coupled multiple-complex coefficient-filter (MCCF). This amalgamation bestows notable advantages. Firstly, from a control perspective, the resultant synchronization technique resembles a quasi-OLS, obviating the need for intricate stability analyses. Moreover, it exhibits commendable disturbances rejection alongside swift dynamic response. Through comprehensive simulation, our proposed technique showcases superiority over existing counterparts, evidencing enhanced settling time, disturbances rejection, and efficiency in the face of frequency drifts.

This is an open access article under the <u>CC BY-SA</u> license.

## Corresponding Author:

Bachir Boumediene L2GEGI Laboratory, Department of Electrical Engineering, Faculty of Applied Sciences University of Tiaret

Tiaret-14000, Algeria Email: bachir.boumediene@univ-tiaret.dz

#### 1. INTRODUCTION

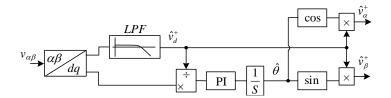

Research in synchronization techniques has recently attracted significant attention thanks to the advances made in small-signal modeling, filtering capability. Point of view control they can be classified into open loops (OLS) and closed loops (CLS) [1]-[31]. The CLS methods are those approaches whose implementation involves feeding back one or more signals, while the OLS are characterized by having no feedback in its structures. The CLS can be categorized into phase locked loops (PLLs), frequency locked loops (FLLs), and other approaches such as least-squares, adaptive observer, and maximum likelihood estimator. The PLLs/FLLs are well recognized in a number of applications such as control of electrical motors, islanding detection, control of converters in more electric aircraft, and vibration suppression in mechanical systems. The pace of developments in the field has accelerated in the last few years, and substantial knowledge has been recently generated. Nevertheless, these two approaches are mathematically equivalent systems. The PLLs are designed to lock the phase angle in synchronous reference frame (SRF), while the FLLs lock the frequency in stationary reference frame. Figure 1 illustrates the block diagram of

Journal homepage: http://beei.org

standard PLLs/FLLs SRF-PLL locked loop and reduced-order generalized integrator frequency locked loop (ROGI-FLL)). The standard techniques have limited filtering capability. The advanced PLLs/FLLs can be understood as conventional SRF-PLL/ROGI-FLL with additional filters. One of the main challenges in these techniques is how to improve dynamic performance without compromising the ability to reject disturbances and stability. On the contrary, the OLS systems benefit from a fast dynamic response and unconditional stability [14]-[31]. This is probably the main advantage of OLS techniques over PLL and FLL ones. The OLS are carried out using classical filters, such as the moving average filter (MAF) and DSC, which results in a frequency-dependent behavior. To deal with this problem, several techniques are recommended, incorporating inverse compensation filter (ICF), predictive filter (PF), and other techniques. The ICF/PF is mathematically equivalent systems. The advanced OLS structures suffer from compromising performances under large frequency drift [14].

Figure 1. Block diagram of the SRF-PLL with LPF

From the discussion, the advanced OLSs and CLSs suffer from almost the same challenges. In response to these challenges, this paper proposes a simple, robust yet fast OLS structure since it does not require a frequency feedback loop. But from a control point of view, it is a quasi (Q)-OLS. The basic building blocks of this technique are the following: i) the multiple-complex coefficient filter (MCCF) is used as a positive and negative sequence extractor (PNSE) since it is mathematically equivalent to real complex filters (RCFs) according to the design framework of reference [17]. On the one hand, the MCCF benefits from a low computational burden under highly distorted voltages, and this is not the case for some PNSEs [17] and ii) an FLL as a parallel frequency detector to adapt the cut-off frequency, which is the originality of this paper. The main advantages of the proposed FLL technique compared to the so-called advanced single-phase FLLs are the following: i) a simple mathematical model based on the linear and recursive form of the voltages. This fact allows the tuning procedure and stability analysis to be straightforward and ii) benefits from a very fast dynamic response and high stability, which is a great advantage, and this is not the case for the so-called advanced phase PLLs/FLLs.

## 2. METHOD

## 2.1. Problem formulation

To overcome the shortcomings of the SRF-PLL from grid unbalance point of view, a low pass filter (LPF) is introduced, as shown in Figure 1 [1]. In this subsection, it is assumed that: i) the estimated frequency is constant; ii) the LPF is of first order; and iii) the cut-off frequency of this LPF and the proportional gain of the PI controller are equal. The transfer function describing the positive components at its input is given by:

$$\frac{\hat{V}_{\alpha\beta}^{+}}{V_{\alpha\beta}} = \frac{k}{(s-j\omega_c)+k} \tag{1}$$

Where

$$\hat{V}_{\alpha\beta}^+(s) = \hat{V}_{\alpha}^+ + j\hat{V}_{\beta}^+$$

and  $V_{\alpha\beta}(s) = V_{\alpha}(s) + jV_{\beta}(s)$

It can be noted that, the complex operator j is produced by cross-coupling between the  $\alpha\beta$  axes. This structure suffers from the following shortcomings: i) only an approximation of the detected amplitude and phase of the positive sequence components and ii) the dynamic response is significantly reduced. On the other hand, to guarantee the dynamic grid voltage support or other related issues, such as the power oscillation elimination under grid fault conditions, the amplitudes of the fundamental positive and negative sequences are required. To deal with these problems, many advanced techniques to extract and separate the positive and negative sequences have been designed by different researchers. Among these, the multiple complex coefficient filter (MCCF), and dual SOGI (DSOGI) [17], are the most investigated techniques. Nevertheless, these two approaches are mathematically equivalent systems [17].

П

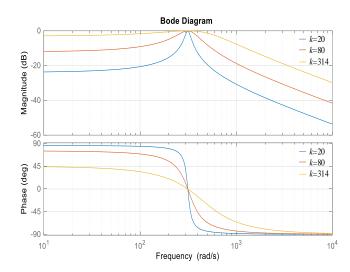

As shown by Figure 2, the frequency response is asymmetrical around zero, which allows distinguishing the negative polarities from the positive ones for the same frequency. The transfer function for obtaining the negative sequence is given by:

$$\frac{\widehat{V}_{\alpha\beta}}{V_{\alpha\beta}} = \frac{k}{(s+j\omega_c)+k} \tag{2}$$

Figure 2. Bode diagram of the SRF-PLL

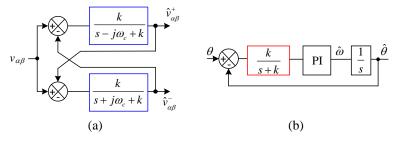

The PNSE in the frequency domain can be expressed as (3):

$$\begin{cases} \hat{V}_{\alpha\beta}^{+}(s) = \frac{k}{s - j\omega_{c} + k} [V_{\alpha\beta}(s) - \hat{V}_{\alpha\beta}^{-}(s)] \\ \hat{V}_{\alpha\beta}^{-}(s) = \frac{k}{s + j\omega_{c} + k} [V_{\alpha\beta}(s) - \hat{V}_{\alpha\beta}^{+}(s)] \end{cases}$$

(3)

Where  $\hat{V}_{\alpha\beta}^{+}(s)$ ,  $\hat{V}_{\alpha\beta}^{-}(s)$  are the estimated positive and negative sequences of  $V_{\alpha\beta}$ , and  $\omega$ c is the cut-off frequency of the PNSE. It is worth to notice that  $k=\omega_{p}$  (cut-off frequency of filters) in the case of the MCCF, while  $k=2\omega_{p}/\omega_{c}$  in the case of DSOGI. The transfer functions describing the input/output of the PNSE are the following:

$$H_1(s) = \frac{k(s+j\omega)}{s^2+2ks+\omega^2}$$

And  $H_2(s) = \frac{k(s-j\omega)}{s^2+2ks+\omega^2}$

Figure 3 presents a schematic diagram of the PNSE, illustrating its operation. Figure 3(a) shows the PNSE, while Figure 3(b) presents the small-signal model of the PNSE. According to  $H_1(S)$ ,  $H_2(S)$  and the linearized model the following observations are made: the dynamics of the PNSE is an LPF with cut off frequency k. The parameter k is a tradeoff between a high filtering capability and fast dynamic response. A small value for k increases, the phase delay and, consequently, degrades the phase margin and dynamic behavior. In [7] the control parameter is selected as a follow: k=331.75 rad/s, k<sub>p</sub>=138.2, and k<sub>i</sub>=7961, which results in phase margin around 45° and settling time of about 2.1 cycles.

Figure 3. Schematic diagram of the PNSE and small signal model of PLL-PNSE: (a) schematic diagram of the PNSE, illustrating the extraction and separation of positive and negative sequences and (b) small signal model depicting the simplified behavior of the PNSE in response to small perturbations

Another disadvantage of these PLLs can also be noticed, they suffer from steady-state phase error during ramp change in frequency with slope  $\Delta \dot{\omega}$  which can be calculated as (4) [3]:

$$\theta_{error} = \sin^{-1}(\frac{\Delta \dot{\omega}}{V k_i}) \tag{4}$$

These shortcomings are the main motivation behind including the proposed single-phase FLL algorithm as a frequency detector instead of a PI loop filter.

#### 2.2. Proposed scheme

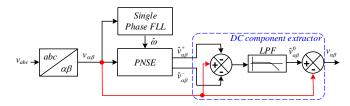

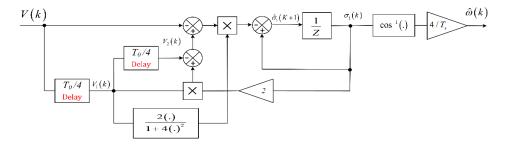

A block diagram of the proposed synchronization technique is provided in Figure 4. The originality of this work is including a simple single phase FLL in the PNSE structure as a secondary frequency detector, which allows obtaining a new Q-OLS structure. Besides, to deal with the dc offset, the extracted positive and negative sequence is subtracted from the grid voltage signal and passed through an LPF to give dc component estimation.

Figure 4. Overall schematic of the proposed technique

## 2.2.1. Basic concept of the proposed frequency locked loop

The proposed approach is based on the linear and recursive form of the voltage. A schematic diagram of this approach is depicted in Figure 5. The single-phase grid voltage can be described as (5):

$$V_{\alpha}(k) = V_{\alpha}^{p} \sin(\omega T_{s} + \phi) \tag{5}$$

Where  $\hat{V}$ ,  $\omega$  and  $\phi$  are the amplitude, pulsation, and phase of the voltage, respectively.

$$V_{\alpha 1}(k) = V_{\alpha}^{p} [\sigma_{1} \sin(\omega k T_{s} + \phi) - \sigma_{2} \cos(\omega k T_{s} + \phi)]$$

$$\tag{6}$$

$$V_{\alpha 2}(k) = V_{\alpha}^{p} [\sigma_{3} \cos(\omega k T_{s} + \phi) - \sigma_{4} \sin(\omega k T_{s} + \phi)]$$

(7)

Where  $\sigma 1 = \cos(\omega T s)/4$ ,  $\sigma 2 = \sin(\omega T s)/4$ ,  $\sigma 3 = \cos(\omega T s)/2$  and  $\sigma 4 = \sin(\omega T s)/2$ . By adding the expressions  $V\alpha 1(k)$  and  $V\alpha 2(k)$  we get.

$$V_{\alpha}(k) + V_{\alpha 2}(k) = 2\sigma_1 V_{\alpha}(k) \tag{8}$$

In (7) is the linear regression model of the grid voltage v(k), which describes the relationship among the grid voltage and its transfer delay signals.  $\sigma 1$  is the unknown parameter related to the grid frequency  $\omega$ . The FLL parameter  $\sigma(k)$  are recursively updated as (9):

$$\sigma(k+1) = \sigma(k) - \frac{2V_{\alpha_1}(k)}{1 + 4V_{\alpha_1}^2(k)} \binom{2\hat{\sigma}_1 V_{\alpha_1}(k) - V_{\alpha}(k)}{-V_{\alpha_2}(k)}$$

(9)

The voltage signal frequency is reconstructed from the parameter  $\sigma_1$ :

$$f = \frac{2}{\pi T} \cos^{-1}(\hat{\sigma}_1) \tag{10}$$

The FLL has full immunity to voltage unbalance and distortion which is a great advantage.

# 2.2.2. Frequency locked loop tuning

To analyze the stability of the proposed FLL, Lyapunov function is selected as (11):

$$V(k) = \tilde{\sigma}^T(k)\tilde{\sigma}(k) \tag{11}$$

$\tilde{\sigma}(k)$  denotes the estimation error and it is defined as (12):

$$\tilde{\sigma}(k) = Z(k) - \sigma(k) \tag{12}$$

Figure 5. Proposed single phase FLL algorithm

The following inequality should be satisfied:

$$V(k)\Delta V(k) < 0 \tag{13}$$

Where  $\Delta V(k)$  denotes the change in Lyapunov function and is given by:

$$\Delta V(k) = V(\tilde{\sigma}(k+1)) - V(\tilde{\sigma}(k)) < 0 \tag{14}$$

Using the dynamics error of the frequency estimator,  $\Delta V$  (k) can be evaluated as (15) and (16):

$$\Delta V(k) = \left| \frac{1}{1 + 4V_{1q}^2(j_1)} \frac{1}{1 + 4V_{1q}^2(j_2)} \dots \frac{1}{1 + 4V_{1q}^2(j_m)} \sigma_1(0) \right|$$

(15)

$$\lim_{k \to \infty} \Delta(V(k)) = 0 \tag{16}$$

Z0 denotes the obtained vector at the perfect convergence.

# 2.2.3. Positive and negative sequence extractor tuning

This subsection demonstrates under which conditions the PNSE exhibits the desired dynamic performance based on the selected parameters. The PNSE with dc offset removal can be obtained as (17):

$$\begin{cases}

\hat{V}_{\alpha\beta0}(s) = \frac{\omega_0}{s + \omega_0} [V_{\alpha\beta}(s) - \hat{V}_{\alpha\beta}^+(s) - \hat{V}_{\alpha\beta}^-(s)] \\

\hat{V}_{\alpha\beta}^+(s) = \frac{k}{s - j\omega_c + k} [V_{\alpha\beta}(s) - \hat{V}_{\alpha\beta}^-(s) - \hat{V}_{\alpha\beta0}(s)] \\

\hat{V}_{\alpha\beta}^-(s) = \frac{k}{s + j\omega_c + k} [V_{\alpha\beta}(s) - \hat{V}_{\alpha\beta}^+(s) - \hat{V}_{\alpha\beta0}]

\end{cases}$$

(17)

Where  $\omega 0$  is the cut-off frequency of the LPF,  $V_{\alpha\beta0}$  are the DC components of  $V\alpha\beta$ . From  $H_1(s)$ ,  $H_2(s)$  and (17) the following observations are made: i)  $H_1(s)$ ,  $H_2(s)$  are in the form of a standard second-order transfer function. Given the compromise between the transient response of the system and the filtering performance, the parameter k is chosen as 314; and ii) from (17), and by performing some simple mathematical manipulations, the transfer function between the dc components and the grid voltage is given as (18):

$$\frac{\hat{v}_{\alpha\beta0}}{v_{\alpha\beta}} = \frac{LPF(s)[1-LPF(s-j\omega_c)]}{1-LPF(s)LPF(s-j\omega_c)} \tag{18}$$

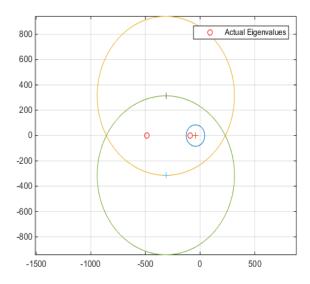

Selecting the value of  $\omega_0$  involves a trade-off between the fast dynamic response and damping since the dynamic of (17) is similar to a first order LPF. A small value of  $\omega_0$  indicates that the dynamic of the PNSE is slow and well-damped. On the contrary, a large value of  $\omega_0$  implies a fast and oscillatory dynamic. To achieve a satisfactory compromise, the value of  $\omega_0$  is set to 40 rad/s and this can be seen on Figure 6. Besides, to evaluate the stability of the system and the transient response, the analysis of the eigenvalues is an effective tool: if all the eigenvalues have negative real parts the system is stable and the transient response depends on the imaginary

parts of the dominant complex conjugate eigenvalues. In addition, the eigenvalues of the left half-plane are far from the imaginary axis, the faster the transient response and this can be seen on Figure 7.

Figure 6. Eigen values diagram

The descriptions of the PNSE state space can be obtained as (19):

$$\begin{cases}

\dot{x} = A(t)x(t) + Bu(t) \\

y = Cx(t)

\end{cases}$$

(19)

Where

$$x(t) = \begin{bmatrix} \hat{V}_{\alpha\beta0} \\ \hat{V}^{+}_{\alpha\beta} \\ \hat{V}^{-}_{\alpha\beta} \end{bmatrix}; u(t) = \begin{bmatrix} V_{\alpha\beta} \\ V_{\alpha\beta} \\ V_{\alpha\beta} \end{bmatrix} A(t) = \begin{bmatrix} -\omega_{0} & -\omega_{0} & -\omega_{0} \\ -k & -k - j\omega_{c} & -k \\ -k & -k - k - j\omega_{c} \end{bmatrix} B(t) = \begin{bmatrix} -\omega_{0} & 0 & 0 \\ 0 & k & 0 \\ 0 & 0 & k \end{bmatrix}.$$

Using the

selection parameters, the eigenvalues obtained are:

$$\lambda 1 = -484.71, \lambda 2 = -91.81, \lambda 3 = -93.83$$

From Figure 6, the selected parameters confirm the stability of the PNSE and allow a fast dynamic response.

# 3. RESULTS AND DISCUSSION

The proposed algorithm is simulated using MATLAB/Simulink three scenarious are investigated: i) frequency step change, ii) frequency ramp change, iii) unbalance under frequency change, and iv) distorted under frequency change. The parameters of the system are listed in Table 1. Some techniques based comparative simulations tests are conducted to highlight the good performance of the enhanced FA-PNSE. ETOLS and CC-ROGI-FLL are selected for the comparison.

Table 1. Grid voltage parameters

Voltage component

FFPS

FFNS

3<sup>rd</sup>

5<sup>th</sup>

7<sup>th</sup>

11 th

Magnitude [PU]

0.733

0.4

0.1

0.1

0.07

0.3

Phase[deg]

5°

50.4°

90°

45°

180°

180°

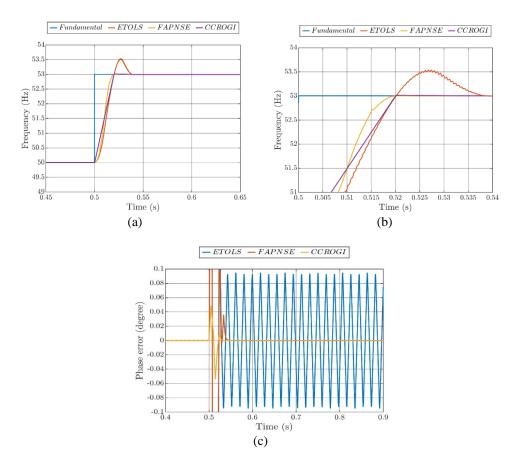

#### 3.1. Frequency step change under normal condition

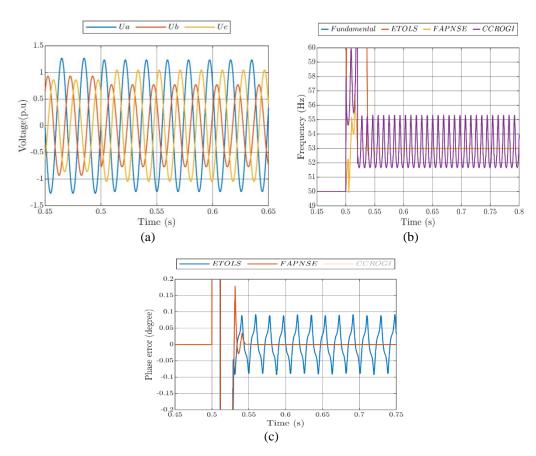

Figure 7 presents simulation results depicting the response of different control systems under a frequency step change. Figure 7(a) illustrates the frequency response of the systems, showcasing their ability to adapt to a jump from 50 to 53 Hz. Figure 7(b) provides a zoomed-in view of the estimated frequencies

during this transition, offering insights into the accuracy and stability of frequency estimation. Figure 7(c) depicts the phase error over time, highlighting how well each system maintains phase synchronization with the grid. Overall, these results indicate that the proposed FA-PNSE exhibits a faster dynamic response compared to ETOLS and CC-ROGI-FLL, with superior settling time and phase angle performance, particularly under off-nominal frequency operation.

Figure 7. Simulation results under frequency step change; (a) frequency, (b) estimated frequency (zoom), and (c) phase error

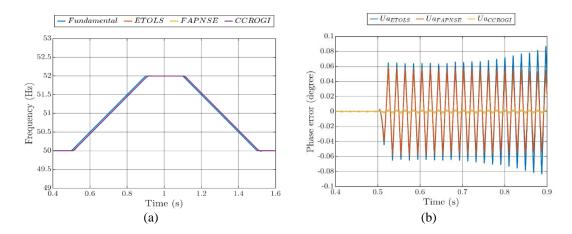

# 3.2. Frequency ramp change under nominal condition

During the test scenario characterized by a frequency ramp change, Figure 8 illustrates the response of the FA-PNSE, ETOLS, and CC-ROGI-FLL systems. Figure 8(a) presents the frequency evolution over time, showcasing how each system adjusts to the ramp change. Meanwhile, Figure 8(b) depicts the phase error for each system throughout the test duration. Observing the results, it is evident that the FA-PNSE, ETOLS, and CC-ROGI-FLL systems exhibit steady-state phase errors of 0.06°, 0.06°, and 0.004° respectively. These findings suggest that while all systems effectively respond to the frequency ramp change, the CC-ROGI-FLL system demonstrates superior phase accuracy compared to the FA-PNSE and ETOLS counterparts.

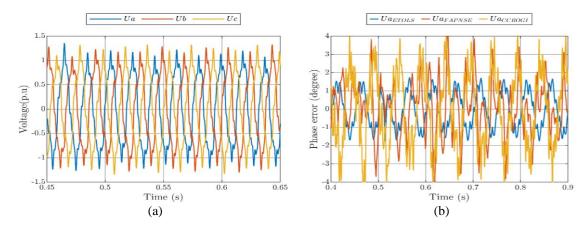

# 3.3. Frequency step change under unbalance

Under the specified test scenario, the system initially operates under unbalanced voltage conditions, characterized by parameters detailed in Table 1. Following this, after a duration of 0.08 seconds, the frequency undergoes a notable increase from 50 to 53 Hz. Figure 9 illustrates the outcomes of this test scenario. In Figure 9(a), the grid voltages are depicted, showcasing the system's response to the unbalanced input conditions. Subsequently, Figure 9(b) portrays the estimated frequency over time, highlighting how each control technique adjusts to the frequency jump. Lastly, Figure 9(c) offers a zoomed-in perspective of the phase error, emphasizing the precision and stability of phase synchronization with the grid. Upon analysis, it becomes evident that the proposed FA-PNSE technique exhibits exceptional performance in rejecting the unbalanced conditions, marked by its swift dynamic response compared to ETOLS. Conversely,

ETOLS demonstrates compromised performance, particularly noticeable in its phase angle behavior under off-nominal grid frequency operation. Furthermore, CC-ROGI-FLL showcases a significant steady-state phase error under these test conditions, indicating potential challenges in maintaining accurate phase synchronization.

Figure 8. Simulation results under frequency ramp change; (a) frequency and (b) phase error

Figure 9. Simulation results under unbalanced conditions; (a) grid voltages, (b) estimated frequency, and (c) phase error zoom

# 4. FREQUENCY STEP CHANGE UNDER DISTORTED SOURCE VOLTAGES

Under the specified test conditions, the system initiates operation under distorted voltage, characterized by parameters outlined in Table 1. Subsequently, after a duration of 0.5 seconds, a significant

frequency jump occurs from 50 to 53 Hz. Figure 10 provides a visual representation of the simulation results under this particular scenario. Figure 10(a) displays the grid voltages, illustrating the system's response to the distorted input conditions. Meanwhile, Figure 10(b) presents the phase error over time, showcasing the discrepancies in phase synchronization with the grid. Analysis of the figure indicates that the proposed FA-PNSE technique, ETOLS, and CC-ROGI-FLL converge to similar outcomes under this test scenario. Notably, all these techniques exhibit a notable steady-state phase error. This observation suggests challenges in maintaining accurate phase synchronization across the board, despite the differences in the applied control techniques.

Figure 10. Simulation results under distorted; (a) grid voltages and (b) phase error

#### CONCLUSION

A synchronization technique for grid integration applications with adaptive frequency estimator parameters has been presented in this paper. The basic building blocks of this synchronization were explained, which are a developed FLL operating together with the PNSE. Moreover, the stability analysis of the PNSE has been presented. The proposed has been investigated with respect to CC-ROGI and ETOLS. Through simulation results, it was demonstrated that the proposed technique provides a fast dynamic response and efficient operation under nominal and off-nominal frequencies.

# REFERENCES

- S. Golestan, A. Vidal, A. G. Yepes, J. M. Guerrero, J. C. Vasquez, and J. Doval-Gandoy, "A true open-loop synchronization technique," IEEE Transactions on Industrial Informatics, vol. 12, no. 3, pp. 1093-1103, Jun. 2016, doi: 10.1109/TII.2016.2550017.

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Three-phase PLLs: a review of recent advances," IEEE Transactions on Power Electronics, vol. 32, no. 3, pp. 1894–1907, Mar. 2017, doi: 10.1109/TPEL.2016.2565642.

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "An open-loop grid synchronization approach for single-phase applications,"

- IEEE Transactions on Power Electronics, vol. 33, no. 7, pp. 5548-5555, Jul. 2018, doi: 10.1109/TPEL.2017.2782622.

S. Golestan, J. M. Guerrero, J. C. Vasquez, A. M. Abusorrah, and Y. Al-Turki, "A study on three-phase FLLs," IEEE Transactions on Power Electronics, vol. 34, no. 1, pp. 213-224, Jan. 2019, doi: 10.1109/TPEL.2018.2826068.

- S. Golestan and J. M. Guerrero, "Conventional synchronous reference frame phase-locked loop is an adaptive complex filter," IEEE Transactions on Industrial Electronics, vol. 62, no. 3, pp. 1679-1682, Mar. 2015, doi: 10.1109/TIE.2014.2341594.

- S. Golestan, J. Guerrero, and J. C. Vasquez, "DCOffset rejection in phase-locked loops: a novel approach," IEEE Transactions on Industrial Electronics, pp. 1-1, 2016, doi: 10.1109/TIE.2016.2546219.

- Z. Chedjara, A. Massoum, P. Wira, A. Safa, and A. Gouichiche, "A fast and robust reference current generation algorithm for three-phase shunt active power filter," International Journal of Power Electronics and Drive Systems (IJPEDS), vol. 12, no. 1, Mar. 2021, doi: 10.11591/ijpeds.v12.i1.pp121-129.

- S. Golestan, M. Monfared, and F. D. Freijedo, "Design-oriented study of advanced synchronous reference frame phase-locked loops," *IEEE Transactions on Power Electronics*, vol. 28, no. 2, pp. 765–778, Feb. 2013, doi: 10.1109/TPEL.2012.2204276.

S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Advantages and challenges of a type-3 PLL," *IEEE Transactions*

- on Power Electronics, vol. 28, no. 11, pp. 4985-4997, Nov. 2013, doi: 10.1109/TPEL.2013.2240317.

- S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero, and J. Doval-Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Transactions on Power Electronics*, vol. 29, no. 12, pp. 6264–6270, Dec. 2014, doi: 10.1109/TPEL.2014.2329917.

- [11] P. Rodriguez, A. Luna, I. Candela, R. Mujal, R. Teodorescu, and F. Blaabjerg, "Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid conditions," IEEE Transactions on Industrial Electronics, vol. 58, no. 1, pp. 127–138, Jan. 2011, doi: 10.1109/TIE.2010.2042420.

- [12] Z. Xin, X. Wang, Z. Qin, M. Lu, P. C. Loh, and F. Blaabjerg, "An improved second-order generalized integrator based quadrature signal generator," *IEEE Transactions on Power Electronics*, vol. 31, no. 12, pp. 8068–8073, Dec. 2016, doi: 10.1109/TPEL.2016.2576644.

[13] P. Kanjiya, V. Khadkikar, and M. S. El Moursi, "Obtaining performance of type-3 phase-locked loop without compromising the benefits of type-2 control system," *IEEE Transactions on Power Electronics*, vol. 33, no. 2, pp. 1788–1796, Feb. 2018, doi: 10.1109/TPEL.2017.2686440.

- [14] E. Guest and N. Mijatovic, "Discrete-time complex bandpass filters for three-phase converter systems," IEEE Transactions on Industrial Electronics, vol. 66, no. 6, pp. 4650–4660, Jun. 2019, doi: 10.1109/TIE.2018.2860554.

- [15] Z. Xin, R. Zhao, F. Blaabjerg, L. Zhang, and P. C. Loh, "An improved flux observer for field-oriented control of induction motors based on dual second-order generalized integrator frequency-locked loop," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 1, pp. 513–525, Mar. 2017, doi: 10.1109/JESTPE.2016.2623668.

- [16] A. Safa, E. M. Berkouk, Y. Messlem, Z. Chedjara, and A. Gouichiche, "A pseudo open loop synchronization technique for heavily distorted grid voltage," *Electric Power Systems Research*, vol. 158, pp. 136–146, May 2018, doi: 10.1016/j.epsr.2018.01.014.

- [17] S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Is using a complex control gain in three-phase FLLs reasonable?," IEEE Transactions on Industrial Electronics, vol. 67, no. 3, pp. 2480–2484, Mar. 2020, doi: 10.1109/TIE.2019.2903748.

- [18] S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Modeling and stability assessment of single-phase grid synchronization techniques: linear time-periodic versus linear time-invariant frameworks," *IEEE Transactions on Power Electronics*, vol. 34, no. 1, pp. 20–27, Jan. 2019, doi: 10.1109/TPEL.2018.2835144.

- [19] X. Wang, L. Harnefors, and F. Blaabjerg, "Unified impedance model of grid-connected voltage-source converters," IEEE Transactions on Power Electronics, vol. 33, no. 2, pp. 1775–1787, Feb. 2018, doi: 10.1109/TPEL.2017.2684906.

- [20] J. Z. Zhou, H. Ding, S. Fan, Y. Zhang, and A. M. Gole, "Impact of short-circuit ratio and phase-locked-loop parameters on the small-signal behavior of a VSC-HVDC converter," *IEEE Transactions on Power Delivery*, vol. 29, no. 5, pp. 2287–2296, Oct. 2014, doi: 10.1109/TPWRD.2014.2330518.

- [21] X. Wang, F. Blaabjerg, and P. C. Loh, "Passivity-based stability analysis and damping injection for multiparalleled VSCs with LCL filters," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8922–8935, Nov. 2017, doi: 10.1109/TPEL.2017.2651948.

- [22] X. Wang and F. Blaabjerg, "Harmonic stability in power electronic-based power systems: concept, modeling, and analysis," *IEEE Transactions on Smart Grid*, vol. 10, no. 3, pp. 2858–2870, May 2019, doi: 10.1109/TSG.2018.2812712.

- [23] L. Harnefors, R. Finger, X. Wang, H. Bai, and F. Blaabjerg, "VSC input-admittance modeling and analysis above the nyquist frequency for passivity-based stability assessment," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 8, pp. 6362–6370, Aug. 2017, doi: 10.1109/TIE.2017.2677353.

- [24] Y. Gui, X. Wang, H. Wu, and F. Blaabjerg, "Voltage-modulated direct power control for a weak grid-connected voltage source inverters," *IEEE Transactions on Power Electronics*, vol. 34, no. 11, pp. 11383–11395, Nov. 2019, doi: 10.1109/TPEL.2019.2898268.

- [25] F. Baradarani, M. R. Dadash Zadeh, and M. A. Zamani, "A phase-angle estimation method for synchronization of grid-connected power-electronic converters," *IEEE Transactions on Power Delivery*, vol. 30, no. 2, pp. 827–835, Apr. 2015, doi: 10.1109/TPWRD.2014.2362930.

- [26] K.-J. Lee, J.-P. Lee, D. Shin, D.-W. Yoo, and H.-J. Kim, "A novel grid synchronization pll method based on adaptive low-pass notch filter for grid-connected PCS," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 1, pp. 292–301, Jan. 2014, doi: 10.1109/TIE.2013.2245622.

- [27] E. Robles, J. Pou, S. Ceballos, J. Zaragoza, J. L. Martin, and P. Ibañez, "Frequency-adaptive stationary-reference-frame grid voltage sequence detector for distributed generation systems," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 9, pp. 4275–4287, Sep. 2011, doi: 10.1109/TIE.2010.2098352.

- [28] Z. Chedjara, A. Massoum, S. Massoum, P. Wira, A. Safa, and A. Gouichiche, "A novel robust PLL algorithm applied to the control of a shunt active power filter using a self tuning filter concept," in 2018 IEEE International Conference on Industrial Technology (ICIT), IEEE, Feb. 2018, pp. 1124–1131, doi: 10.1109/ICIT.2018.8352336.

- [29] S. Biricik, S. Redif, Ö. C. Özerdem, S. K. Khadem, and M. Basu, "Real-time control of shunt active power filter under distorted grid voltage and unbalanced load condition using self-tuning filter," *IET Power Electronics*, vol. 7, no. 7, pp. 1895–1905, Jul. 2014, doi: 10.1049/iet-pel.2013.0924.

- [30] A. Malkhandi and T. Ghose, "A fourier-based single phase PLL algorithm: Design, analysis, and implementation in FPGA controller," *International Transactions on Electrical Energy Systems*, vol. 27, no. 10, Oct. 2017, doi: 10.1002/etep.2410.

- [31] D. Dong, B. Wen, D. Boroyevich, P. Mattavelli, and Y. Xue, "Analysis of Phase-Locked Loop Low-Frequency Stability in Three-Phase Grid-Connected Power Converters Considering Impedance Interactions," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 1, pp. 310–321, Jan. 2015, doi: 10.1109/TIE.2014.2334665.

## **BIOGRAPHIES OF AUTHORS**

Bachir Boumediene born on October 20, 1976, in Tiaret, Algeria, is an accomplished electrical engineer with a profound dedication to advancing sustainable transportation solutions. Graduating from Ibn Khaldoun University in 1998, he later obtained his Majister in Techniques and Spatiales in 2008 before completing his doctorate in 2021. Rising through the ranks, he now holds the esteemed position of full professor at the Department of Science and Technology, University of Tiaret. His research focuses primarily on electric vehicle charging and diagnostics. He can be contacted at email: bachir.boumediene@univ-tiaret.dz and boumediene.bachir@univ-tiaret.dz.

Rabah Araria was born on October 6, 1979, in Tiaret, Algeria. He earned his degree in electrical engineering, specializing in electromechanics, from Ibn Khaldoun University in Tiaret (Algeria) in 2007, and subsequently completed his doctorate in 2020 at the same institution. In 2020, he joined the Department of Science and Technology as an associate professor and was promoted to full professor in 2022. His specific areas of interest include the charging and diagnostics of electric vehicles. Correspondence Address: Department of Electrical Engineering/Laboratory: L2GEGI, University of Tiaret, P.O. 78 Zaaroura, Tiaret-14000, Algeria. He can be contacted at email: rabah.araria@univ-tiaret.dz.

Belkacem Mekhloufi (b) [3] So born December 27, 1970, is an expert in soil sciences and environmental studies. Having obtained his master's degree in soil sciences in 2010, followed by a doctorate in soil sciences and environmental studies in 2022. His research focuses on renewable energy sources and the environment. He can be contacted at email: mekhloufi.belkacem@univ-tiaret.dz.

Patrice Wira received the M.Sc. degree and the Ph.D. degree in Electrical Engineering from the University of Haute Alsace, Mulhouse, France, in 1997 and 2002, respectively. He received the Accreditation to Supervise Research (the French Habilitation a Diriger des Recherches) in Computer Sciences from the University of Haute Alsace in 2009. He was an Associate Professor with the MIPS Laboratory (Laboratoire Modelisation, Intelligence, Processus, Systeme) at the University of Haute Alsace. Since 2011, he is a Full Professor. He is author or coauthor of more than 20 technical papers covering his research interests from artificial neural networks for the modeling and simulation of complex automation systems, neuro-control approaches, to adaptive control systems. He can be contacted at email: patrice.wira@uha.fr.